台积电官方也在次技术研讨会上进一步向未接披露了2nm工艺计划★★◆◆★■,其将在2nm工艺节点引入新型的 GAAFET 结构★■,即门全包围场效应晶体管(Gate-All-Around FET)结构。台积电官方表示,这种结构可以进一步提高晶体管密度和性能,并且降低功耗和泄漏。

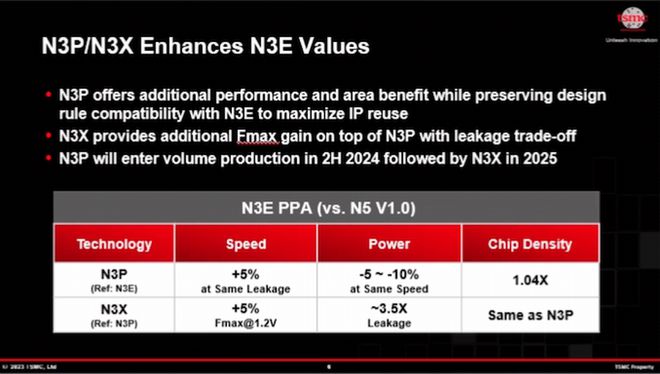

台积电官方表示,目前其规划的3nm工艺家族有如下版本,分别是基础的N3、成本优化的N3E、性能提升的N3P★■■■、为高性能计算设备使用的N3X■★◆、为车载设备准备的更为高压耐受的N3 AE。

台积电介绍称★◆★★,相较于 N3E 制程技术★■◆◆,N2技术可在相同功耗下■★◆,性能最快增加 15%;在相同频率下,功耗可降低 30%,同时晶片密度增加逾 15%◆★◆■★■。而这一N2工艺将会在2025年进入量产。

N3X则是优考虑HPC应用的性能和最大时钟频率■★。 因此其与N3P相比■◆■,N3X在驱动电压为1■■■.2V的情况下其速度提高了5% ,芯片密度与N3P相同。

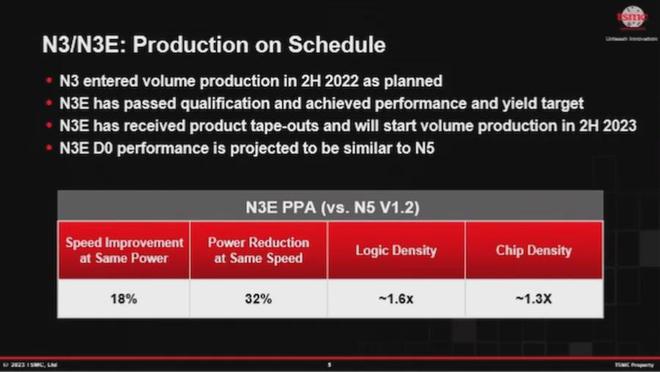

根据了解,台积电旗下的N3E工艺相比较现阶段的台积电5nm工艺,可在相同频率下降低 32% 的功耗,或者在相同功耗下提高 18% 的性能。而N3P则可在相同频率下相比较于N3E降低5-10%的功耗,在同功耗的情况下提升5%的性能■■■★◆■。

台积电给出的时间表指出,其将在2023年推出基础N3工艺以及N3E工艺的产品,2024年推出2024年推出N3P工艺相关产品,N3X和N3AE(N3A)将会在2025年进行推出。

N3AE则是面向汽车领域的工艺■■◆★◆■,其具备有更强的可靠性,台积电表示将提供到相关的3nm开发SDK工具帮助开发厂商设计相关产品,并争取在2025年带来可在汽车上可靠使用的N3A工艺。